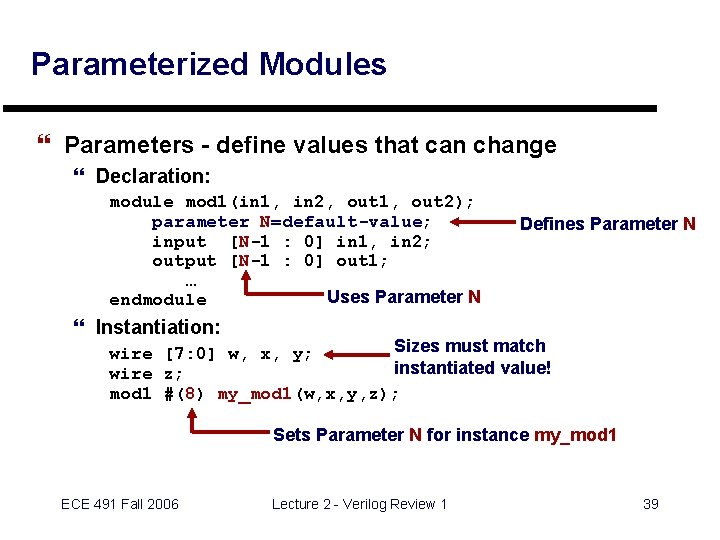

Parameter Parameters must be defined within module boundaries using the keyword parameter A parameter is a constant that is local to a module that can optionally be redefined on an instance Parameters are typically used to specify the width of variables and time delays Parameter example A `define is a global macro It is of global scope If you define in a module, it still stays declared after the module After it is defined, is referenced using the macro name with a preceding ` (backtic) character It can exist either inside or outside of a module declaration, and both are treated the sameVerilog01 internal wire declaration requirements are discussed in the next section 4 Verilog01 `default_nettype none As noted in section 2, 1bit internal wires driven from continuous assignments had to be explicitly declared in Verilog1995 Verilog01 removed this inconsistency from the Verilog language Verilog01 also

System Verilog Macro A Powerful Feature For Design Verification Projects

Verilog ifdef parameter

Verilog ifdef parameter-Overriding parameters Parameters can be overridden with new values during module instantiation The first part is the module called design_ip by the name d0 where new parameters are passed within # ( ) The second part is use a Verilog construct called defparam to set the new parameter values The first method is commonly used to pass new parameters in RTL designsThe 'ifdef, 'else, and 'endif directives allow the conditional inclusion of code Themacrosthatareargumentstothe'ifdefdirectivescanalsobe defined in the Verilog source file by use of the'definedirective In that case, there is no change in the invocation of the HDL Compiler to read in Verilog files Example 93 shows a design that

Prezentaciya Na Temu Verilog System Tasks Functions And Compiler Directives Ando Ki Spring 09 Skachat Besplatno I Bez Registracii

Verilog generate statement is a powerful construct for writing configurable, synthesizable RTL It can be used to create multiple instantiations of modules and code, or conditionally instantiate blocks of code However, many Verilog programmers often have questions about how to use Verilog generate effectivelyChecks that a Verilog `endif directive is followed by a comment that matches the name of the opening `ifdef or `ifndef See Style endifcomment 2> Can I use parameters to check in the " `ifdef line" I understand that this sounds stupid as the name sugegsts "if defined" and I can imagine "define" is only thorugh "`define", nevertheless nothing harm in getting it clarified from experts Thanks again PS I am using VerilogXL Kind Regards, Srini

Answer (1 of 4) code`define SYNTHESIS // Uncommented for synthesis (`define method 1) //`define SIMULATION //Uncommented for simulation `include some_headerv The defined parameter value can be changed in two ways module instantiation and defparam statement In each module instance, we can override the parameter values at compile time we can override the single parameter value or multiple parameter values also The Eda playground example for single parameters override in Verilog STYLE_NO 1Example 2 Parameterized register model Verilog01 style 4 Parameters and Parameter Redefinition When instantiating modules with parameters, in Verilog1995 there are two ways to change the parameters for some or all of the instantiated modules;

GNU Emacs (VerilogMode)) module m (`ifdef c_input c, `endif /*AUTOARG*/ // Inputs a, b) input a;Parameters must be defined within module boundaries using the keyword parameter A parameter is a constant that is local to a module that can optionally be redefined on an instancebyinstance basis For parameterized modules, one or more parameter declarations typically precede the port declarations in a Verilog1995 style model, such as the Verilog adds default parameter values There are cases where this is useful, however it remains to be seen how widely used and supported this will become Verilog requires the ` in front of all macro calls While some have proposed this be eliminated in Verilog 12(ish), the ` provides major advantages I would hate to lose the

Setting Compiler Options

Verilog Tutorial 3 Define Text Macros Youtube

This page contains Verilog tutorial, Verilog Syntax, Verilog Quick Reference, PLI, modelling memory and FSM, Writing Testbenches in Verilog, Lot of Verilog Examples and Verilog in One Day Tutorial `ifdef Optionally includes lines of source code during compilation The `ifdef directive checks that a macro has been defined, and if so One can use `ifdef `endif to check whether the macro is defined or not Moreover, one can use an optional generate block to test the value of macro/parameters Moreover, one can use an optional generate block to test the value of macro/parametersReg30 counter = 0;

Ece 491 Senior Design I Lecture 2 Verilog

Systemverilog Is Getting Even Better Sunburst Define Ifdef Else Include Timescale Wire Reg Integer Real Systemverilog Is Getting Even Better An Update On The Proposed 09 Pdf Document

I have a parameterised module in verilog, where the parameters are a clock rate and refresh rate, which is used to calculate how many cycles of inactivity are inserted between instances of a repeating operation However, it is very easy to set parameters that cannot be attained (because the operation takes a nontrivial length of time, so theVerilog Compiler Directives macro_code // parameterized macro `undef macro_name // undefine a macro `ifdef macro_name1 // include source lines1 if macro_name1 is defined // the source lines1 `elsif macro_name2 // any number of elsif clauses, the first defined // macro_name includes the source lines `else `ifdef SUB_IS_A_FOOBAR `define SUB_CELL foobar `else `define SUB_CELL foobiz `endif `SUB_CELL subcell (/*AUTOINST*/);

Chapter 42 Tips And Tricks

System Verilog Macro A Powerful Feature For Design Verification Projects

Conditional Compilation (#if, #ifdef, #ifndef, #else, #elif,

0 件のコメント:

コメントを投稿